Categories

- Analyzers->

- ¬ Logic Analyzers->

- ¬ 0-18 Ch

- ¬ 24-32 Ch

- ¬ 34-61 Ch

- ¬ 64-68 Ch

- ¬ 70-102 Ch

- ¬ 136-768 Ch

- ¬ 1768-8160 Ch

- ¬ Network Analyzers->

- ¬ Noise Figure Analyzers->

- ¬ Optical Spectrum Analyzers->

- ¬ PIM Analyzers->

- ¬ Serial Data Analyzers->

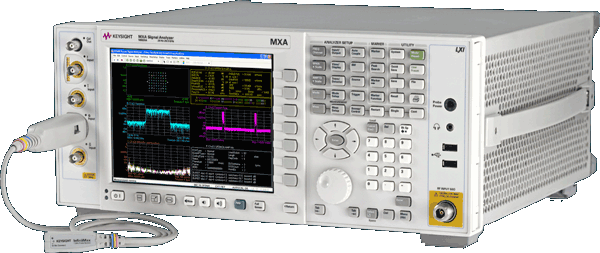

- ¬ Spectrum Analyzers->

- Generators->

- Meters->

- Oscilloscopes->

- Power Testing->

- Other->

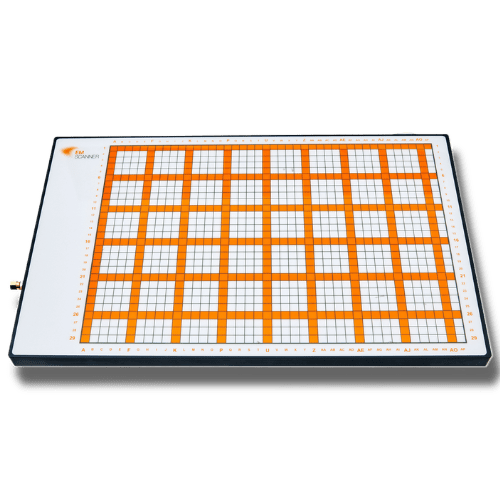

- EMC EMI->

Manufacturers

Testimonials

-

★★★★★

"Fantastic deal. The oscilloscope is in very good condition. Packed for shipment to survive anything"Jeff

-

★★★★★

"Premium equipment. Excellent communication. Fast. Best value!"Avi

-

★★★★★

"Practically in new condition"Darcy

-

★★★★★

"There was a small issue; The people at BRL Test were 100% responsive and issue resolved. Thanks!"Mike

-

★★★★★

"Best packing ever! I would let you ship one of my children!"Todd

-

★★★★★

"Unit received in great shape. Passed Agilent calibration. Good job!!"Lee

-

★★★★★

"In every aspect these guys are great!"Sarah

Join our Newsletter

Your IP Address is: 216.73.217.72